задумал поменять стоковый дисплей TCG057QV1AC-G10 5.7" на что-то подобное, но c большей диагональю 7.5" и с учетом того, что LCD-контроллер EPSON S1D113742 останется прежним, т.к. находится на материнской плате...

Суть моего приглашения к обсуждению в следующем:

поэтому вопрос:

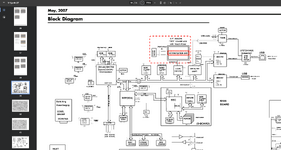

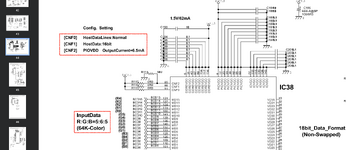

- а как вычислить способность OS менять режим работы QVGA/VGA? что бы зря не питать иллюзий, в поиске нового LCD? т.к. меня смутила информация в SM про FPC-сокет pin #32 (скрин стр.44 SM с осликом ИА - подчеркнуто красным) о имеющем место переключениии VGA/QVGA ч/з H/L-импульс... (вроде бы как may be!)

- или всетаки можно учитывать тот факт, что без взлома OS - контроллер самостоятельно не справися с разрешением VGA (640x480) или как указано у него в дата шите "up ot WVGA (800x480)"?

- может кто даст свои рекомендации при выборе TFT LCD, на что обратить внимание?

Суть моего приглашения к обсуждению в следующем:

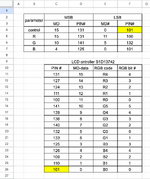

- меня смущает что в спецификации на железо указана совсем другая модель монитора KCG057QV1DB-G00 у которого 20-pinout (ну да бог с ним!), плюс в specs указана инфа на одно разрешение экрана QVGA = 320x240;

- в спецификации на рабочий LCD контроллер пишут о VGA = 640x480 и до WVGA = 800x480 (это все LCD контроллер умеет делать, но нет инфы про QVGA) и пока все отлично работает! значит где есть пробел в информации на устройства...

- в тех списках Kyocera вариантов с 7.5" с QVGA нет вообще... поэтому пытаюсь выяснить способность к адаптации OS между QVGA и VGA - продумали инженеры Roland эту способность или нет?

- TCG075VGLEAANN-GN00-SA (подходит по FPC-pinout. но из-за его габаритов (толщины) - могут быть проблемы с установкой в стесненное пространство коробки синта)

- TCG075VGLDA-G20 (подходит по механическим характеристика как slim-девайс, но есть ньюансы со 40-pin шлейфом (+LED-supply), которые придется решать путем JST/FPC переходника и попыткой впихнуть 2 шлейфа в 1 сокет)

поэтому вопрос:

- а как вычислить способность OS менять режим работы QVGA/VGA? что бы зря не питать иллюзий, в поиске нового LCD? т.к. меня смутила информация в SM про FPC-сокет pin #32 (скрин стр.44 SM с осликом ИА - подчеркнуто красным) о имеющем место переключениии VGA/QVGA ч/з H/L-импульс... (вроде бы как may be!)

- или всетаки можно учитывать тот факт, что без взлома OS - контроллер самостоятельно не справися с разрешением VGA (640x480) или как указано у него в дата шите "up ot WVGA (800x480)"?

- может кто даст свои рекомендации при выборе TFT LCD, на что обратить внимание?

Вложения

Последнее редактирование: